# DIMEtalk 3.1 Reference Guide

NT108-0305 - Issue 7

#### **Contacting Nallatech:**

## Support:

www:

Go to www.nallatech.com and click 'support'.

Email:

support@nallatech.com

#### Phone/Fax

**Europe and Asia-Pacific:** Phone: +44 (0)1236 789500

### WWW:

www.nallatech.com

**North America** Phone: +1-877-44-NALLA

Document Name: DIMEtalk 3.1 Reference Guide

Document Number: NT108-0305

Issue Number: Issue 7

Date of Issue: 26/02/07

**Revision History:**

| Date       | Issue Number | Revision                                                                                           |

|------------|--------------|----------------------------------------------------------------------------------------------------|

| 06/04/2006 | 2            | Initial release of 3.1                                                                             |

|            |              | New to 3.1 Reference Guide:                                                                        |

|            |              | "BenBLUE-III Clock Deskew Module for Use with ZBT SRAM" on page 52,                                |

|            |              | "Clock Deskew Component for BenBLUE Modules" on page 83,                                           |

|            |              | "DIME-C Link FIFO" on page 93,                                                                     |

|            |              | "DDR2 Memory Clocks Module" on page 102,                                                           |

|            |              | "DDR-II SRAM Memory Nodes" on page 104,                                                            |

|            |              | "BenDATA-V4 SDRAM Memory Node" on page 113,                                                        |

|            |              | "BenDATA2 SDRAM Clock Module" on page 126,                                                         |

|            |              | "BenDATA2 SDRAM Memory Node - 333MHz" on page 128,                                                 |

|            |              | "PCI-X Clocks Driver Component" on page 84,                                                        |

|            |              | "PCI-X Host Interface" on page 4,                                                                  |

|            |              | "Grounding Extra BenBLUE-III Control Pins" on page 53,                                             |

|            |              | "ZBT SRAM Testbench for Simulation" on page 55,                                                    |

|            |              | "Host Testbench" on page 11,                                                                       |

|            |              | New section on component placement - "How to Place Components in DIMEtalk Networks" on page 140.   |

| 06/09/2006 | 3            | Updates for DIMEtalk 3.1.1                                                                         |

|            |              | "PCI-X Host Interface" on page 4:                                                                  |

|            |              | Hostusr_clk signal removed from component block diagram and description table.                     |

|            |              | "PCI-X Clocks Driver Component" on page 84:                                                        |

|            |              | HostlfClocks: hostif_clk200 signal added.                                                          |

|            |              | "DDR2 Memory Clocks Module" on page 102:                                                           |

|            |              | DDR2CoreClocks now DDR2CoreClocks0, DDR2CoreClocks1, DDR2CoreClocks2, DDR2CoreClocks3.             |

|            |              | Simplified connection of network components in the following examples:                             |

|            |              | "BenDATA-V4 Memory Components" on page 140,                                                        |

|            |              | "PCI-X Edge and PCI-X Clock Components" on page 141,                                               |

|            |              | "PCI-X SRAM Component" on page 141,                                                                |

|            |              | "BenBLUE-V4 Memory Components" on page 143.                                                        |

|            |              | New component added:                                                                               |

|            |              | "PCI-X Module Clocks Driver Component" on page 88.                                                 |

|            |              | "DDR2 Memory Clocks Module" on page 102 contains the following, previously undocumented parameter: |

|            |              | Use_with_DDRII_SDRAM (listed in Table 95).                                                         |

|            |              | New section added on the use of clocks on the BenNUEY-PCI-X-V4:                                    |

|            |              | "DIMEtalk Clock Usage on the BenNUEY-PCI-X-V4" on page 146.                                        |

| Date       | Issue Number | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18/10/2006 | 4            | Updates for DIMEtalk 3.1.2<br>Updates to "PCI-X Host Interface" section:<br>Figure 2 updated<br>Table 4 updated<br>Table 5 updated<br>Component Definition also updated.<br>Updates to "Clock Deskew Component" section:<br>Table 38 updated<br>Updates to "DDR-II SRAM Memory Nodes" section:<br>Table 101 updated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22/11/2006 | 5            | Updates for DIMEtalk 3.1.3<br>Change to section "DIMEtalk Clock Usage on the BenNUEY-PCI-X-V4":<br>Clock C does not have to be used on the PCI-X motherboard as specified in sub-<br>section "Non Virtex-4 Modules Populated on a BenNUEY-PCI-X-V4 Mother-<br>board". Section updated with correct usage information.<br>Changes to section "DDR-II SRAM Memory Nodes":<br>Table 98 updated with new entry for BenNUEY-PCI-104-V4,<br>Correction to Table 98 to show correct entry for 'IDELAY_CTRLS' value for<br>'ddr2sram_32_benbluev4_sec' entry,<br>Table 101 updated with list of support files for the BenNUEY-PCI-104-V4 plus cor-<br>rections to 'idelay_calibrate.vhd' and 'sram_data_iobs.vhd' entries. New entry<br>'sram_data_path.vhd' added.<br>Table 102 updated with correct device usage information for all entries.<br>"Generic Settings" updated with BenNUEY-PCI-104-V4 details. |

| 27/11/06   | 6            | New components added as follows:<br>"H100 PCI-X Clocks Driver Module", "H100 DDR2 SDRAM Memory Node",<br>"DDR Asynchronous Bridge", "DDR Asynchronous Bridge Clock Components"<br>and "H100 Host Interface".<br>New section added on usage of new components - "H100 Components".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26/02/2007 | 7            | <ul> <li>Updates for DIMEtalk 3.1.5</li> <li>"DIMEtalk Detailed Design" section revised with new VHDL attributes information for DIMEtalk components.</li> <li>Note added to "DDR2 Memory Clocks Module" on use of component with H100 series hardware.</li> <li>New components added as follows:</li> <li>"DIME-C Internal LinkFIFO (dclink_fifo)" and "DIMEtalk DDR to MGT Bridge".</li> <li>Removed "DDR Asynchronous Bridge Clock Components" section - component no longer used.</li> <li>Revised Table 84 with external MGT link information for H100 System Clock component.</li> <li>Removed MGT Interface example from "H100 Components" section, updated example available in HPC Software Toolkit User Guide.</li> </ul>                                                                                                                                                                    |

#### Intellectual Property

The contents of this document are the copyright of Nallatech Limited - © Nallatech Limited 2007. All rights reserved. The product name, Nallatech, the Nallatech logo, "The High Performance FPGA Solutions Company", DIMEtalk, DIMEscript, DIME, DIME-II and FUSE are all trade marks of Nallatech Limited. All names, images and logos identifying Nallatech Limited or third parties and their products and services are subject to copyright, design rights and trade marks of Nallatech Limited and/or third parties. Nothing contained in these terms shall be construed as conferring by implication, estoppel or otherwise any licence or right to use any trademark, patent, design right or copyright of Nallatech Limited, or any other third party. Microsoft and Windows are either registered trade marks or trade marks of Microsoft Corporation in the United States and/or other countries.

#### Disclaimer

This document is for general information purposes only and is not tailored for any specific situations or circumstances. Although Nallatech Limited believes the contents to be true and accurate as at the date of writing, Nallatech Limited makes no assurances or warranty regarding the accuracy, currency or applicability of any contents in relation to specific situations and particular circumstances. As such, the content should not be relied upon and readers should not act on this information without further consultation with Nallatech Limited. Nallatech Limited accepts no responsibility for loss which may arise as a result of relying on the information in this document alone.

#### Copyright ©1993 - 2007 Nallatech Limited

**All Rights Reserved**

This page intentionally blank

# Contents

| About this Reference Guide                                                      |    |  |

|---------------------------------------------------------------------------------|----|--|

| DIMEtalk Component Descriptions                                                 |    |  |

| Edges                                                                           |    |  |

| PCI Host Interface                                                              |    |  |

| PCI-X Host Interface                                                            |    |  |

| USB Host Interface                                                              |    |  |

| Ethernet Host Interface                                                         |    |  |

| Host Testbench                                                                  |    |  |

| Simulation Support                                                              | 13 |  |

| Xilinx Simulation Libraries for ModelSim XE                                     |    |  |

| Xilinx Simulation Libraries for ModelSim SE/PE                                  |    |  |

| H100 Host Interface                                                             |    |  |

| Basic Internal FPGA Nodes                                                       |    |  |

| Block RAM Node                                                                  |    |  |

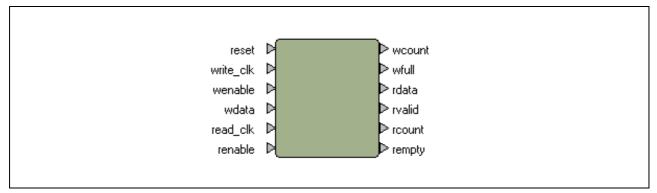

| Read FIFO                                                                       |    |  |

| Write FIFO                                                                      |    |  |

| Memory Map Node                                                                 |    |  |

| FIFO Loopback                                                                   |    |  |

| Memory Map Loopback                                                             |    |  |

| Master DIMEtalk Node                                                            |    |  |

| ZBT Nodes                                                                       |    |  |

| ZBT Memory Node 32-Bit                                                          |    |  |

| ZBT Memory Node 64-Bit                                                          |    |  |

| Clock Deskew Component<br>BenBLUE-III Clock Deskew Module for Use with ZBT SRAM |    |  |

|                                                                                 |    |  |

| Grounding Extra BenBLUE-III Control Pins                                        |    |  |

| ZBT SRAM Testbench for Simulation                                               |    |  |

| Bridges                                                                         |    |  |

| 4-Bit Bidirectional Physical Bridge                                             |    |  |

| 8-Bit Bidirectional Physical Bridge                                             |    |  |

| 16-Bit Bidirectional Physical Bridge<br>32-Bit Bidirectional Physical Bridge    |    |  |

| 4-Bit Bidirectional Asynchronous Bridge                                         |    |  |

| 8-Bit Bidirectional Asynchronous Bridge                                         |    |  |

|                                                                                 |    |  |

|   | 16-Bit Bidirectional Asynchronous Bridge                      | .67  |

|---|---------------------------------------------------------------|------|

|   | 32-Bit Bidirectional Asynchronous Bridge                      | . 69 |

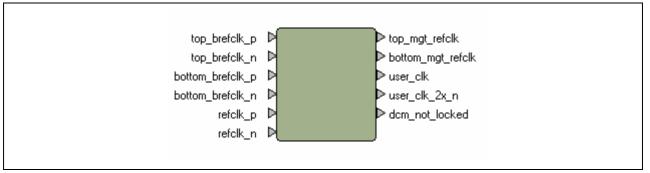

|   | RocketIO Bridge                                               | 71   |

|   | RocketIO Clock Component                                      | .73  |

|   | DIMEtalk DDR to MGT Bridge                                    | 76   |

|   | Routers                                                       | 77   |

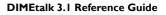

|   | Router - Reconfigurable Four Way Non-blocking                 | 77   |

|   | System                                                        | .81  |

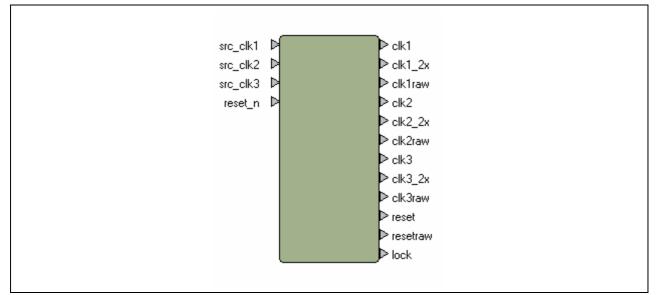

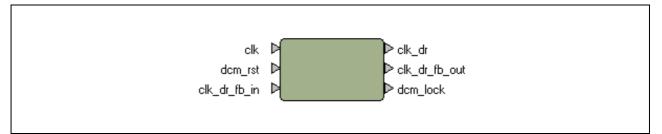

|   | Clock Driver                                                  | 81   |

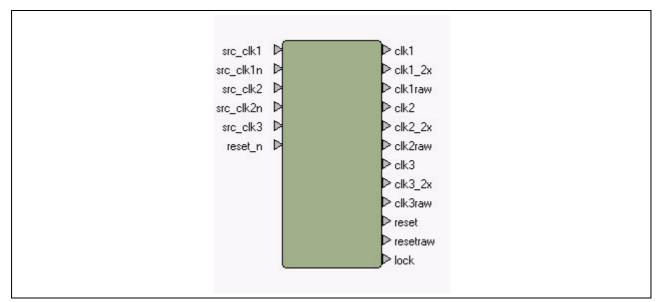

|   | Clock Deskew Component for BenBLUE Modules                    | 83   |

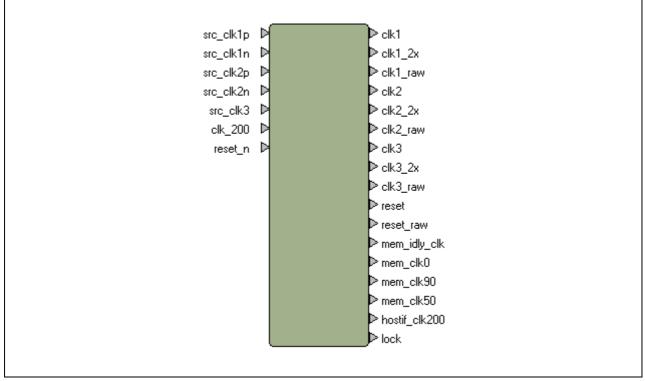

|   | PCI-X Clocks Driver Component                                 | 84   |

|   | PCI-X Module Clocks Driver Component                          | .88  |

|   | H100 PCI-X Clocks Driver Module                               | 89   |

|   | DIME-C                                                        |      |

|   | DIME-C Link FIFO                                              | .93  |

|   | DIME-C External MGT LinkFIFO (dimec_ddr2mgtlinkfifo)          | 95   |

|   | DIME-C Internal LinkFIFO (dclink_fifo)                        | .98  |

|   | Virtex-4 DDR2 Memory                                          | 102  |

|   | DDR2 Memory Clocks Module                                     |      |

|   | DDR-II SRAM Memory Nodes                                      |      |

|   | BenDATA-V4 SDRAM Memory Node                                  | 113  |

|   | HI00 DDR2 SDRAM Memory Node                                   |      |

|   | DDR SDRAM                                                     |      |

|   | BenDATA2 SDRAM Clock Module                                   |      |

|   | BenDATA2 SDRAM Memory Node - 333MHz                           |      |

|   | BenDATA2 SDRAM Memory Node - 400MHz                           |      |

|   | How to Place Components in DIMEtalk Networks                  | 140  |

|   | BenDATA-V4 Memory Components                                  |      |

|   | PCI-X Edge and PCI-X Clock Components<br>PCI-X SRAM Component |      |

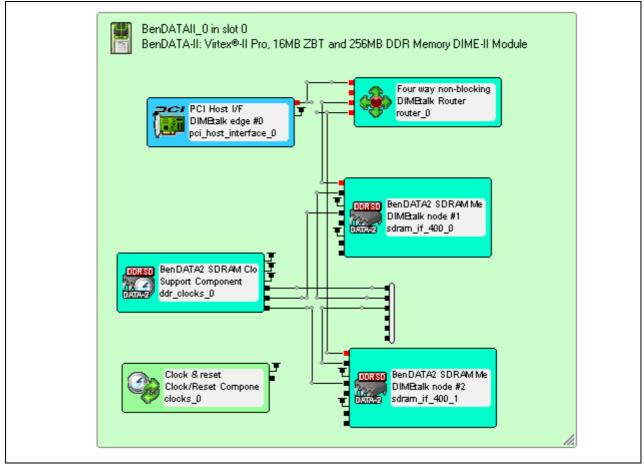

|   | BenDATA-II Memory and Clock Components                        |      |

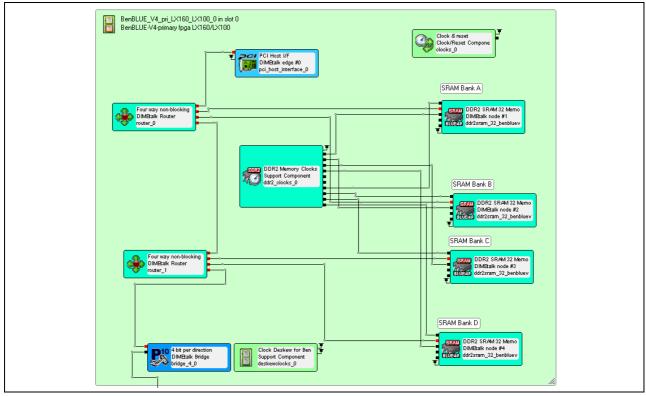

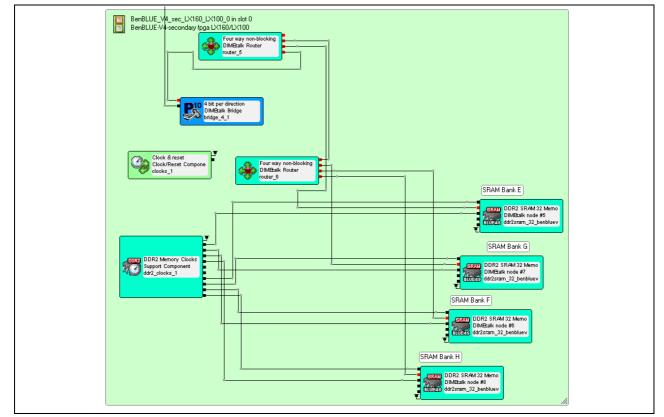

|   | BenBLUE-V4 Memory Components                                  |      |

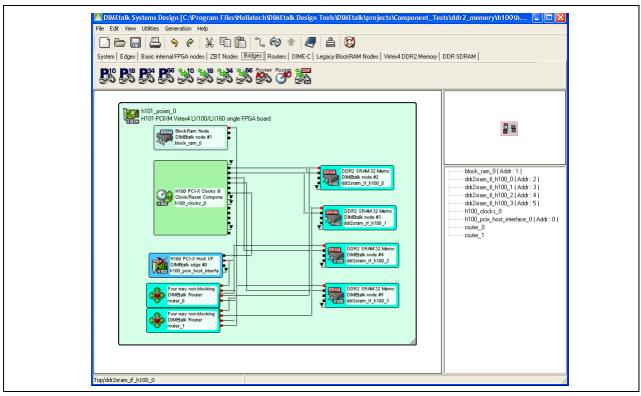

|   | HI00 Components                                               | 145  |

| _ | DIMEtalk Clock Usage on the BenNUEY-PCI-X-V4                  |      |

| D | IMEtalk Detailed Design                                       |      |

|   | Data Packet Format                                            |      |

|   | Overview                                                      |      |

|   | Request Packets<br>Response Packets                           |      |

|   | Capability Registers                                          |      |

|   | Transport Format Description                                  |      |

|   | •                                                             |      |

| dtinfo VHDL Attributes for User Components | .156 |

|--------------------------------------------|------|

| dtinfo Attributes Description              |      |

| dtinfo Attributes Example                  | 159  |

This page intentionally blank

# **List of Figures**

| Figure I:PCI Host Interface Component                            |    |

|------------------------------------------------------------------|----|

| Figure 2:PCI-X Host Interface Component                          | 4  |

| Figure 3: USB Host Interface Component                           | 7  |

| Figure 4:Ethernet Host Interface Component                       | 9  |

| Figure 5:Host Testbench                                          |    |

| Figure 6:H100 Host Interface Component                           |    |

| Figure 7:Block RAM Node Component                                | 16 |

| Figure 8:Block RAM Waveform                                      |    |

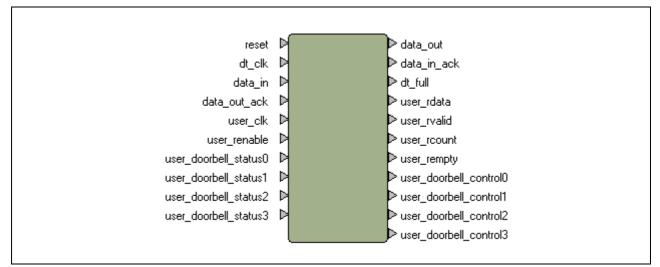

| Figure 9:Read FIFO Component                                     | 19 |

| Figure 10:Read FIFO User Access                                  | 22 |

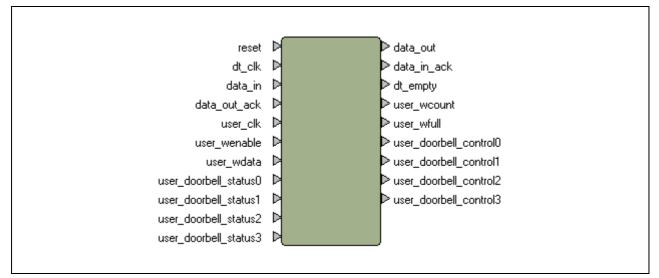

| Figure 11:Write FIFO Component                                   | 22 |

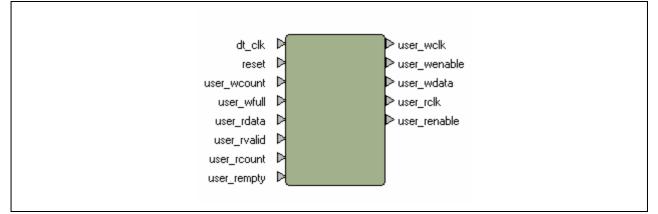

| Figure 12:Write FIFO User Access                                 | 25 |

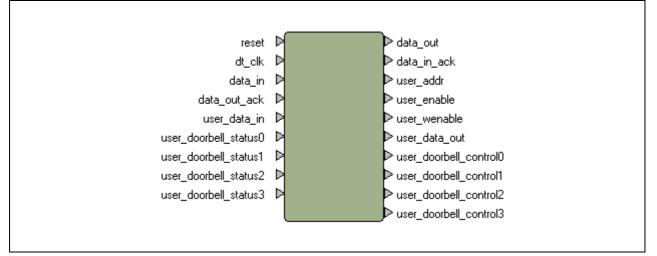

| Figure 13:Memory Map Node Component                              |    |

| Figure 14:Memory Map Write                                       |    |

| Figure 15:Memory Map Read                                        |    |

| Figure 16:FIFO Loopback Component                                | 29 |

| Figure 17:Memory Map Loopback                                    | 31 |

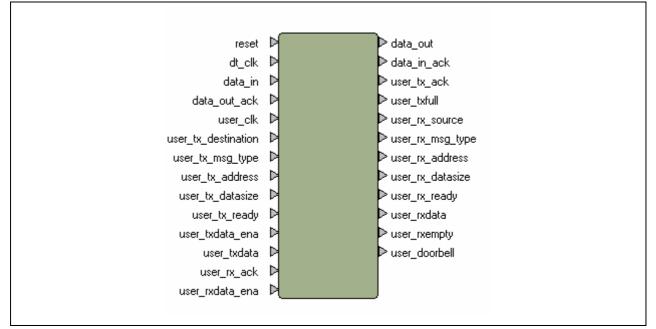

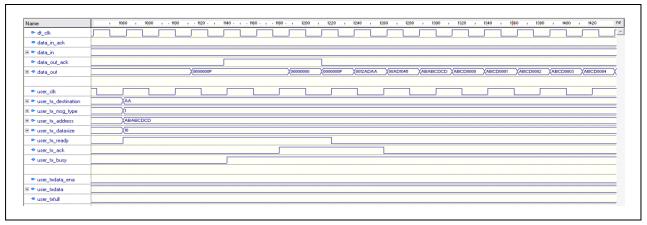

| Figure 18:Master DIMEtalk Node                                   | 33 |

| Figure 19:Master Node: tx data write (16 data words)             |    |

| Figure 20:Master Node: tx data to destination                    |    |

| Figure 21:Master Node: write packet - no response (5 data words) |    |

| Figure 22:Master Node: rx data                                   | 41 |

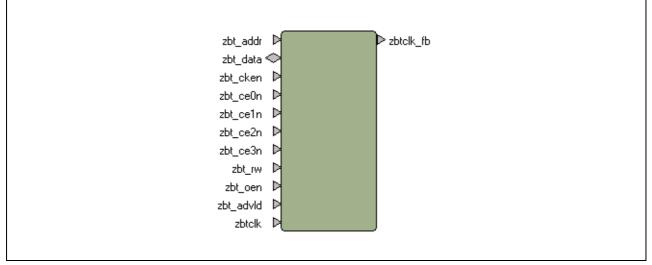

| Figure 23:ZBT 32-Bit Interface Component                         |    |

| Figure 24:ZBT Write Access                                       | 45 |

| Figure 25:ZBT Read Access                                        |    |

| Figure 26:ZBT 64-Bit Interface Component                         |    |

| Figure 27:Clock Deskew Module Component                          | 49 |

| Figure 28:BenBLUE-III Clock Deskew Module                        | 52 |

| Figure 29:Grounding Extra BenBLUE-III Control Pins Component     | 53 |

| Figure 30:ZBT SRAM Testbench for Simulation Component            | 55 |

| Figure 31:4-bit Bridge Component                                 |    |

| Figure 32:8-Bit Bridge Component                                 | 58 |

| Figure 33:16-Bit Bridge Component                                |    |

| Figure 34:32-Bit Bridge Component                                |    |

| Figure 35:4-Bit Bridge Component                                 |    |

| Figure 36:8-Bit Bridge Component                                 |    |

| Figure 37:16-Bit Bridge Component                                |    |

| Figure 38:32-Bit Bridge Component                                | 69 |

| Figure 39:RocketIO Bridge Component                              | 71 |

| Figure 40:RocketIO Component                                     | 74 |

| Figure 41:DIMEtalk DDR to MGT Bridge Component                   | 76 |

| Figure 42:Router Component                            |     |

|-------------------------------------------------------|-----|

| Figure 43:Clock Driver Module                         |     |

| Figure 44:Clock Deskew Component for BenBLUE Module   |     |

| Figure 45:PCI-X Clocks Driver Component               |     |

| Figure 46:PCI-X Module Clocks Driver Component        |     |

| Figure 47:H100 PCI-X Module Clocks Driver Component   |     |

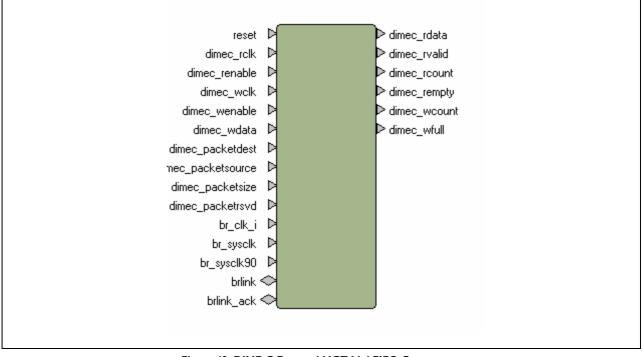

| Figure 48:DIME-C Link FIFO Component                  |     |

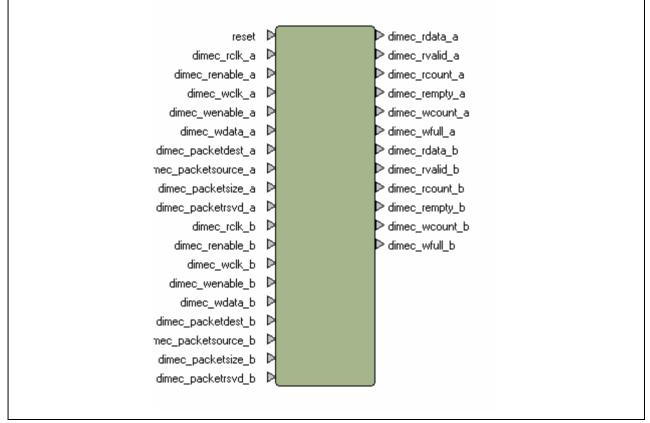

| Figure 49:DIME-C External MGT LinkFIFO Component      |     |

| Figure 50:DIME-C Internal LinkFIFO Component          |     |

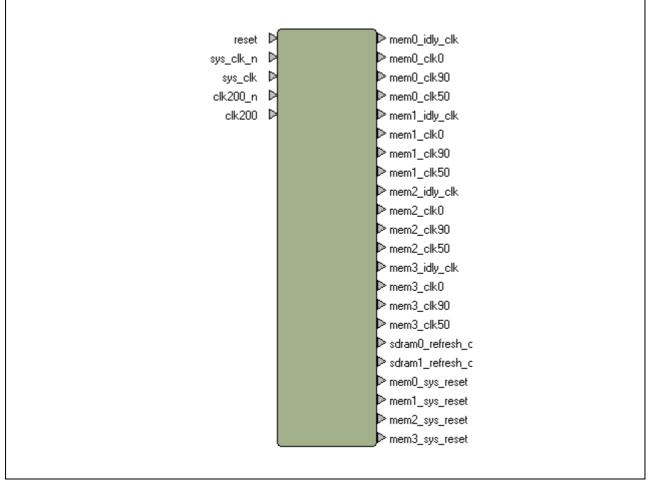

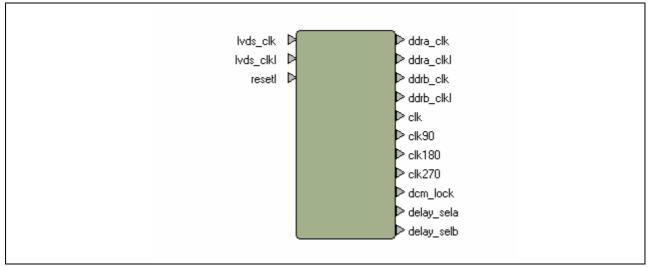

| Figure 51:DDR2 Memory Clocks Module Component         |     |

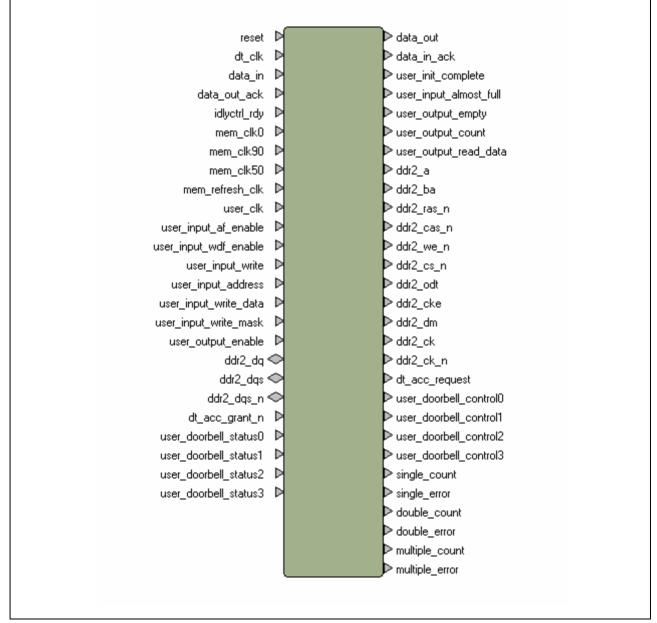

| Figure 52:DDR-II SRAM Memory Node                     | 105 |

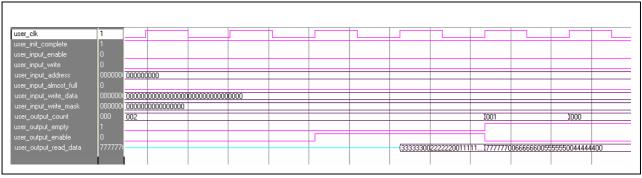

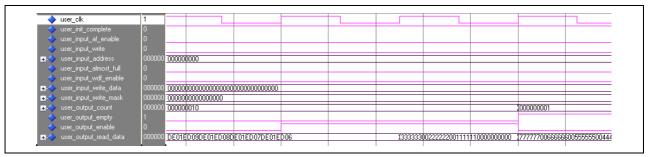

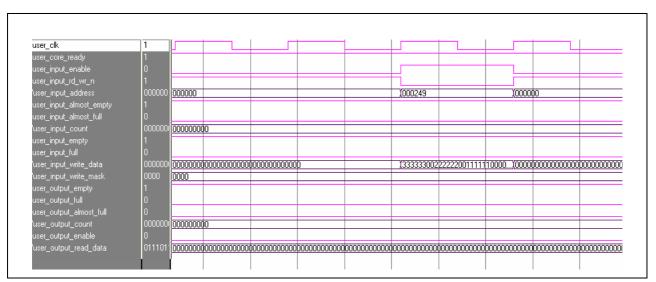

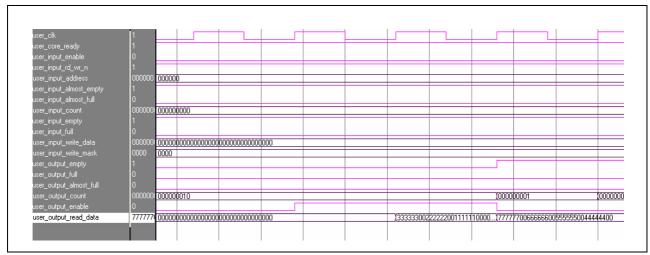

| Figure 53:DDR-II SRAM Writes                          |     |

| Figure 54:DDR-II SRAM Reads                           | 112 |

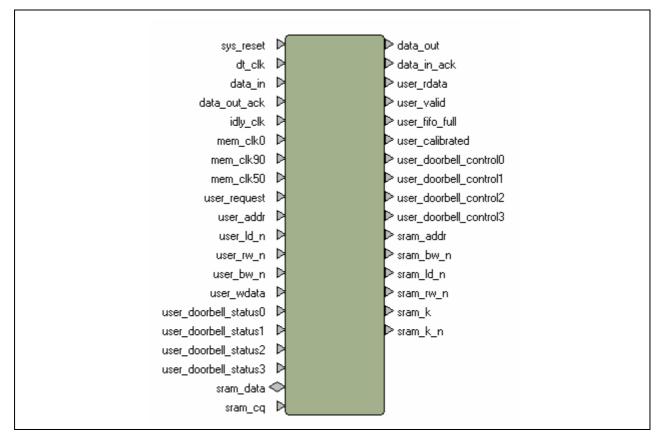

| Figure 55:BenDATA-V4 SDRAM Memory Node                | 113 |

| Figure 56:Write Command                               | 119 |

| Figure 57:Read Command                                |     |

| Figure 58:Read Data                                   |     |

| Figure 59:H100 DDR2 SDRAM Memory Node                 | 121 |

| Figure 60:Write Command                               | 125 |

| Figure 61:Read Command                                | 125 |

| Figure 62:Read Data                                   | 125 |

| Figure 63:benDATA2 SDRAM Clock Module Component       |     |

| Figure 64:benDATA2 SDRAM Memory Node - 333MHz         | 129 |

| Figure 65:Write Command                               | 134 |

| Figure 66:Read Command                                | 135 |

| Figure 67:Read Data                                   | 135 |

| Figure 68:benDATA2 SDRAM Memory Node - 400MHz         | 136 |

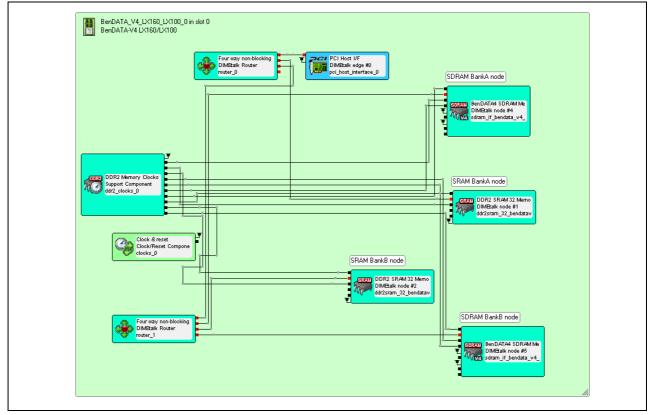

| Figure 69:Virtex-4 DDR2 Memory Components             | 140 |

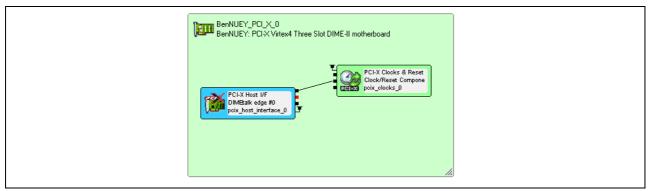

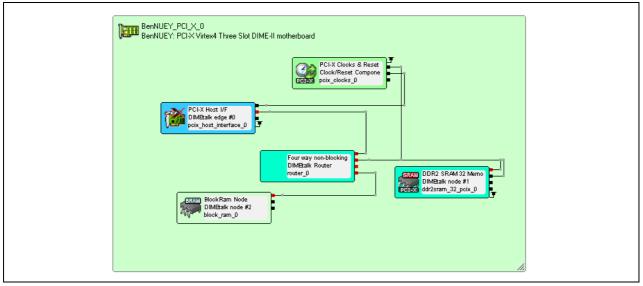

| Figure 70:PCI-X Edge and PCI-X Clock Components       |     |

| Figure 71:PCI-X SRAM Component                        | 141 |

| Figure 72:BenDATA-II Memory and Clock Components      | 142 |

| Figure 73:BenBLUE-V4 Primary FPGA Memory Component    |     |

| Figure 74:BenBLUE-V4 Secondary FPGA Memory Component  | 144 |

| Figure 75:H100 DDR-II SRAM Component                  |     |

| Figure 76:H100 DDR2 SDRAM Component                   | 146 |

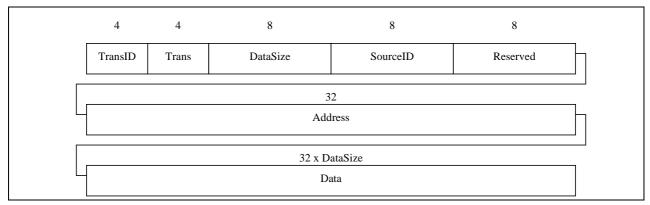

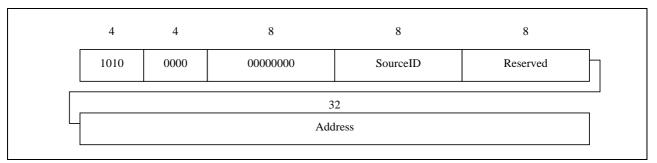

| Figure 77:DIMEtalk Request Packets Bit Stream Format  | 149 |

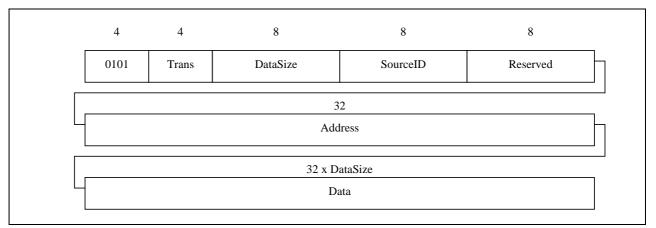

| Figure 78:DIMEtalk Read Packet Format                 | 150 |

| Figure 79:DIMEtalk Write Packet Format                | 151 |

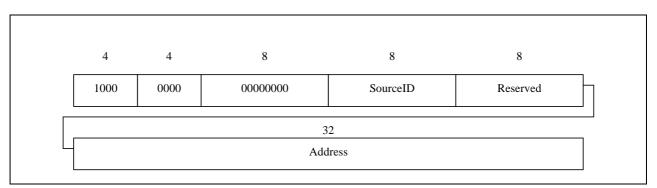

| Figure 80:DIMEtalk Maintenance Packet Format          | 151 |

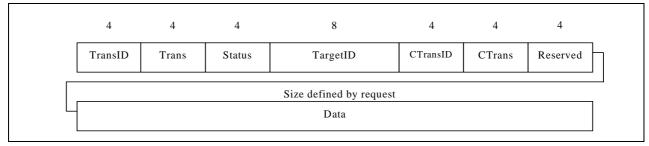

| Figure 81:DIMEtalk Doorbell Packet Format             | 152 |

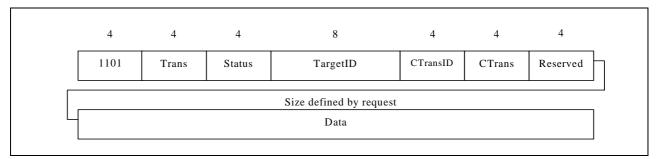

| Figure 82:DIMEtalk Response Packets Bit Stream Format |     |

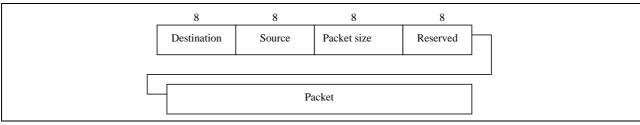

| Figure 83:DIMEtalk Response Packet Type 13 Format     |     |

| Figure 84:Transport Header Packet Bit Stream Format   |     |

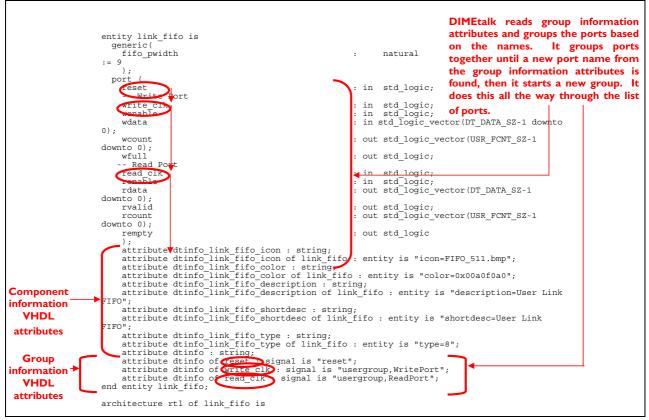

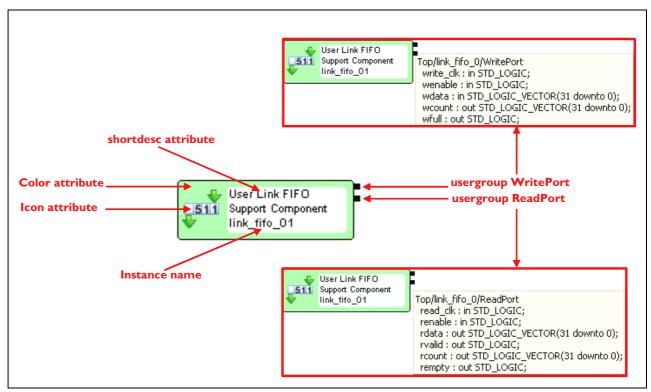

| Figure 85:Link FIFO VHDL Example                      |     |

| Figure 86:Attributes of Link FIFO DIMEtalk Component  |     |

# List of Tables

| Table I:FUSE Naming Conventions                   | xix |

|---------------------------------------------------|-----|

| Table 2:PCI Host Signal Descriptions              | 2   |

| Table 3:PCI Host Signal Support Files             | 3   |

| Table 4:PCI-X Host Interface Signal Descriptions  |     |

| Table 5:PCI-X Host Signal Support Files           | 5   |

| Table 6:USB Host Interface Signal Descriptions    | 8   |

| Table 7:USB Host Interface Support Files          |     |

| Table 8:Ethernet Host Signal Descriptions         | 10  |

| Table 9:Ethernet Host Interface Support Files     | 10  |

| Table 10:Host Testbench Signal Descriptions       |     |

| Table 11:Host Testbench Support Files             | 12  |

| Table 12:H100 Host Interface Signal Descriptions  | 14  |

| Table 13:H100 Host Interface Support Files        | 5   |

| Table 14:Block RAM Signal Descriptions            | 16  |

| Table 15:Block RAM User Generics                  | 17  |

| Table 16:Block RAM Support Files                  |     |

| Table 17:Read FIFO Signal Descriptions            | 20  |

| Table 18:Read FIFO User Generics                  |     |

| Table 19:Read FIFO Support Files                  | 21  |

| Table 20:Write FIFO Signal Descriptions           | 23  |

| Table 21:Write FIFO User Generics                 | 24  |

| Table 22:Write FIFO Support Files                 | 24  |

| Table 23:Memory Map Signal Descriptions           | 26  |

| Table 24:Memory Map Support Files                 | 27  |

| Table 25:FIFO Loopback Signal Descriptions        | 29  |

| Table 26:FIFO Loopback Support Files              | 30  |

| Table 27:Memory Map Loopback Signal Descriptions  | 31  |

| Table 28:Memory Map Loopback Support Files        | 31  |

| Table 29:Master Node Signal Descriptions          | 33  |

| Table 30:Master Node Support Files                | 34  |

| Table 31:ZBT 32-Bit Interface Signal Descriptions | 42  |

| Table 32:ZBT 32-Bit Interface User Generics       |     |

| Table 33:ZBT 32-Bit Interface Support Files       | 44  |

| Table 34:ZBT 64-Bit Interface Signal Descriptions | 46  |

| Table 35:ZBT 64-Bit Interface User Generics       | 47  |

| Table 36:ZBT 64-Bit Interface Support Files       | 48  |

| Table 37:Clock Deskew Signals                     |     |

| Table 38:Clock Deskew User Generics               | 50  |

| Table 39:Clock Deskew Support Files               |     |

| Table 40:BenBLUE-III Clock Deskew Signals         | 52  |

| Table 41:BenBLUE-III Clock Deskew Support Files   |     |

| Table 42:BenBLUE-III Clock Deskew Signals                   | 54 |

|-------------------------------------------------------------|----|

| Table 43:BenBLUE-III Clock Deskew Support Files             | 54 |

| Table 44:ZBT SRAM Testbench for Simulation Signals          | 55 |

| Table 45:ZBT SRAM Testbench for Simulation Support Files    | 56 |

| Table 46:4-Bit Bridge Signal Descriptions                   |    |

| Table 47:4-Bit Bridge Support Files                         | 57 |

| Table 48:8-Bit Bridge Signal Descriptions                   | 59 |

| Table 49:8-Bit Bridge Support Files                         | 59 |

| Table 50:16-Bit Bridge Signal Descriptions                  |    |

| Table 51:16-Bit Bridge Support Files                        | 61 |

| Table 52:32-Bit Bridge Signal Descriptions                  |    |

| Table 53:32-Bit Bridge Support Files                        |    |

| Table 54:4-Bit Bridge Signal Descriptions                   |    |

| Table 55:4-Bit Bridge Support Files                         |    |

| Table 56:: 8-Bit Bridge Signal Descriptions                 | 65 |

| Table 57:8-Bit Bridge Support Files                         | 66 |

| Table 58:16-Bit Bridge Signal Descriptions                  | 67 |

| Table 59:16-Bit Bridge Support Files                        | 68 |

| Table 60:32-Bit Bridge Signal Descriptions                  |    |

| Table 61:32-Bit Bridge Support Files                        |    |

| Table 62:RocketIO Bridge Signal Descriptions                | 71 |

| Table 63:RocketIO Bridge User Generics                      |    |

| Table 64:RocketIO Bridge Support Files                      |    |

| Table 65:RocketIO Clocks Signal Descriptions                | 74 |

| Table 66:RocketIO Generics                                  |    |

| Table 67:RocketIO Clocks Support Files                      | 75 |

| Table 68:DIMEtalk DDR to MGT Bridge Signals                 | 76 |

| Table 69:DIMEtalk DDR to MGT Bridge User Generics           |    |

| Table 70:DIMEtalk DDR to MGT Bridge Support Files           | 77 |

| Table 71:Router Signal Descriptions                         | 78 |

| Table 72:Router User Generics                               | 79 |

| Table 73:Router Support Files                               | 79 |

| Table 74: Clock Driver Signals                              | 81 |

| Table 75: Clock Driver User Generics                        | 82 |

| Table 76:Clock Driver Support Files                         | 82 |

| Table 77: Clock Deskew for BenBLUE Signals                  | 83 |

| Table 78:Clock Deskew for BenBLUE Support Files             | 84 |

| Table 79:PCI-X Clocks Driver Component Signals              | 85 |

| Table 80:PCI-X Clocks Driver Component Support Files        | 86 |

| Table 81:PCI-X Module Clocks Driver Component               |    |

| Table 82:PCI-X Module Clocks Driver Component Support Files | 89 |

| Table 83:H100 PCI-X Module Clocks Driver User Generics      |    |

| Table 84:H100 PCI-X Module Clocks Driver Signals            | 91 |

| Table 85:H100 PCI-X Module Clocks Driver Support Files      |    |

| Table 86:DIME-C Link FIFO Signals                           |    |

| Table 87:DIME-C Link FIFO Support Files                     |    |

| Table 88:DIME-C Link FIFO User Generics                     |    |

|                                                             |    |

| Table 89:DIME-C External MGT LinkFIFO Signals                                                                | 96  |

|--------------------------------------------------------------------------------------------------------------|-----|

| Table 90:DIME-C External MGT LinkFIFO Support Files                                                          |     |

| Table 91:DIME-C External MGT LinkFIFO User Generics                                                          |     |

| Table 92:DIME-C Internal LinkFIFO Signal Descriptions                                                        |     |

| Table 93:DIME-C Internal LinkFIFO User Generics                                                              |     |

| Table 94:DIME-C Internal LinkFIFO Support Files                                                              | 101 |

| Table 95:DDR2 Memory Clocks Module User Generics                                                             | 103 |

| Table 96:DDR2 Memory Clocks Module Signals                                                                   | 103 |

| Table 97:DDR2 Memory Clocks Module Support Files                                                             |     |

| Table 98:Supported DDR-II Top Levels                                                                         | 104 |

| Table 99:DDR-II SRAM Memory Node User Generics                                                               | 105 |

| Table 100:DDR-II SRAM Memory Node Signal Descriptions                                                        | 106 |

| Table 101:DDR-II SRAM Memory Node Support Files - Common Between Implementations                             |     |

| Table 102:DDR-II SRAM Memory Node Support Files - Individual for Each Implementation                         | 108 |

| Table 103:BenDATA-V4 SDRAM Memory Node User Generics                                                         |     |

| Table 104:BenDATA-V4 SDRAM Memory Node Signals                                                               |     |

| Table 105:BenDATA-V4 SDRAM Memory Node Support Files                                                         | 117 |

| Table 106:H100 DDR2 SDRAM Memory Node User Generics                                                          |     |

| Table 107:H100 DDR2 SDRAM Memory Node Signals                                                                |     |

| Table 108:H100 DDR2 SDRAM Memory Node Support Files                                                          |     |

| Table 109:BenDATA2 SDRAM Clock Module User Generics                                                          |     |

| Table 110:BenDATA2 SDRAM Clock Module Signals                                                                | 127 |

| Table 111:BenDATA2 SDRAM Clock Module Support Files                                                          | 127 |

| Table 112:BenDATA2 SDRAM Memory Node - 333MHz User Generics                                                  |     |

| Table 113:BenDATA2 SDRAM Memory Node - 333MHz Signals                                                        |     |

| Table 114:BenDATA2 SDRAM Memory Node - 333MHz Support Files                                                  |     |

| Table 115:BenDATA2 SDRAM Memory Node - 400MHz User Generics                                                  |     |

| Table 116:BenDATA2 SDRAM Memory Node - 400MHz Signals                                                        |     |

| Table 117:BenDATA2 SDRAM Memory Node - 400MHz Support Files                                                  |     |

| Table 118:Example Designs with Required Clocks Components         Table 119:Request Packet Field Definitions |     |

| Table 120:Trans Values for Reads                                                                             |     |

| Table 121:Trans Values for Writes                                                                            |     |

| Table 122:Doorbell Read Conditions                                                                           |     |

| Table 122:Doorbell Write Conditions                                                                          |     |

| Table 124:Response Packet Field Definitions                                                                  |     |

| Table 125:Status Values for Response Packets                                                                 |     |

| Table 126:Response Packet Type 13 Format                                                                     |     |

| Table 127:DIMEtalk Capability Register                                                                       |     |

| Table 128:Packet Capability Register Bits                                                                    |     |

| Table 129:Request packet type 2 Capability Register Bits                                                     |     |

| Table 130:Request packet type 5 Capability Register Bits                                                     |     |

| Table 131:Transport Layer Header                                                                             |     |

| Table 132:DIMEtalk General Component Attributes - Descriptions                                               |     |

| Table 133:DIMEtalk Signal Group Attributes - Descriptions                                                    |     |

| -                                                                                                            |     |

This page intentionally blank

# About this Reference Guide

# Using this manual

This Reference Guide provides detailed information on DIMEtalk components and the data packet formats used in the software. The manual is designed to provide reference information for users of DIMEtalk and should be read in conjunction with the *DIMEtalk User Guide*.

- For information on how to use the software see the DIMEtalk User Guide.

- For additional application notes please visit <u>www.nallatech.com/applicationnotes.</u>

- For information on using the DIMEtalk Application Program Interface (API) see the FUSE C-C++ API Developer's Guide.

# Symbols Used

Throughout this manual there are symbols to draw attention to important information:

The red arrow symbol indicates a set of procedures to follow, such as installing software or setting up hardware.

The blue 'i' symbol indicates useful or important information.

The red '!' symbol indicates a warning, which requires special attention.

# **Reference Guide Format**

The Reference Guide is divided into **Sections**. The sections divide the document as follows:

- DIMEtalk Component Descriptions: The individual components including descriptions, block diagrams and, where relevant, wave forms.

- DIMEtalk Detailed Design: Information on DIMEtalk packet formats and VHDL attributes for user components.

# **Related Nallatech Documentation**

| • | Nallatech | BenDATA-II Reference Guide |

|---|-----------|----------------------------|

|---|-----------|----------------------------|

- Nallatech BenDATA-V4 Reference Guide

- Nallatech Connecting FPGAs in DIMEtalk Application Note

- Nallatech DDR SDRAM Controller Core Datasheet

- Nallatech DIME-C User Guide

- Nallatech

DIMEtalk User Guide

- Nallatech

FUSE C-C++ API Developer's Guide

- Nallatech FUSE System Software User Guide

- Nallatech IEEE754 Floating Point Core User Guide

- Nallatech Tcl Plug-In for FUSE Developer's Guide

- Xilinx Xilinx Synthesis and Verification Design Guide

- Xilinx Application Note XAPP645

# **Abbreviations**

- API: Application Program Interface

- DAC: Digital-to-Analog Converter

- DIME: DSP and Image Processing Modules for Enhanced FPGAs

- ECC: Error Correction Control

- FIFO: First In First Out stack memory

- FIR: Finite Impulse Response

- **FPGA:** Field Programmable Gate Array

- FUSE: Field Upgradeable System Environment

- IDE: Integrated Development Environment

- I/O: Input/Output

- PCI: Peripheral Component Interconnect

- SRAM: Static Random Access Memory

- TCP/IP: Transmission Control Protocol/Internet Protocol

- UCF: User Constraints File

- USB: Universal Serial Bus

- VHDL: VHSIC Hardware Description Language

# **Typographical Conventions**

The following typographical conventions are used in this manual:

• Red text indicates a cross-reference to information within the document set you are currently reading. Click the red text to go to the referenced item. To return to the original page, right-click anywhere on the current page and select **Go To Previous View**.

- <u>Blue underlined text</u> indicates a link to a Web page. Click blue-underlined text to browse the specified Web site.

- Italics denotes the following items:

- References to other documents:

See the FUSE System Software User Guide for more information.

- Emphasis in text:

Enable Loopback should not be enabled until all other registers have been set up.

# FUSE Naming Conventions

Please note that the DIMEtalk clocks are named differently in the FUSE System Software compared to this Reference Guide. The clock naming conventions are shown in Table 1.

| Clock Names in FUSE   | Clock Names in Documentation |

|-----------------------|------------------------------|

| System Clock (SYSCLK) | Clock A (CLK A)              |

| DSP Clock (DSPCLK)    | Clock B (CLK B)              |

| Pixel Clock (PIXCLK)  | Clock C (CLK C)              |

Table I: FUSE Naming Conventions

# **Comments and Suggestions**

At the back of this Reference Guide, you will find a remarks form. We welcome any comments you may have on our product or its documentation. Your remarks will be examined thoroughly and taken into account for future versions of Nallatech products.

This page intentionally blank

# Section I

# DIMEtalk Component Descriptions

In this section the following DIMEtalk components are described:

- Edges

- Basic Internal FPGA Nodes

- ZBT Nodes

- Bridges

- Routers

- System

- DIME-C

- Virtex-4 DDR2 Memory

- DDR SDRAM

This section also explains how to use the following components:

- BenDATA-V4 memory components

- PCI-X edge and clock components

- BenDATA-II memory and clock components

- BenBLUE-V4 memory components

- HI00 components

- DIMEtalk Clock Usage on the BenNUEY-PCI-X-V4

# I.I Edges PCI Host Interface

# **Functional Description**

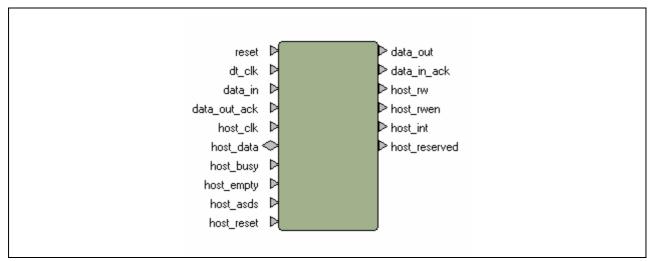

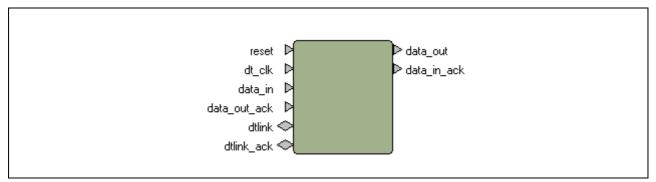

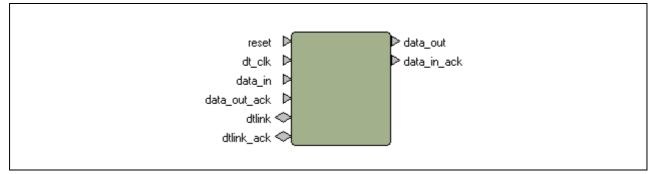

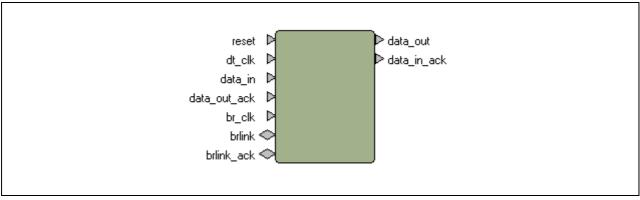

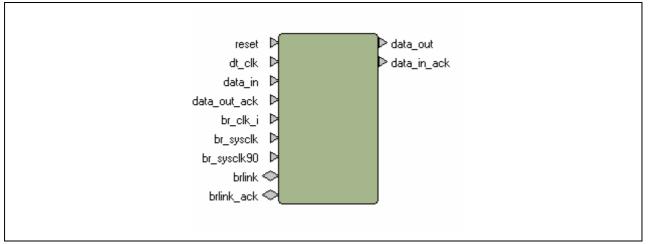

This component handles the interface between a PCI host and a DIMEtalk network on Nallatech PCI cards (e.g. BenNUEY). The interface is assumed to be clocked by CLK2. This edge component converts data being transferred into the CLK1 domain. On a multi-FPGA motherboard such as the BenNUEY, the Host Data signals should be mapped to PCI\_COMMS(0:31) whilst the Host Control signals should be mapped to PCI\_COMMS(32:39). If this interface is instantiated on a module plugged into a BenONE motherboard the Host Data signals should be mapped to LBUS(0:31) whilst the Host Control signals should be mapped to ADJOUT(0:7). The PCI Host Interface signals are shown in Figure 1 and described in Table 2.

Figure I: PCI Host Interface Component

## **S**ignals

The signal descriptions are provided in Table 2.

| Group        | Туре                              | Signal<br>Description | Width  | Direction |

|--------------|-----------------------------------|-----------------------|--------|-----------|

| reset        | DIMEtalk reset                    | reset                 | l-bit  | In        |

| dt_clk       | DIMEtalk network clock. Def. CLKI | dt_clk                | l-bit  | In        |

| DIMEtalk     |                                   | data_in               | 32-bit | In        |

| DIMEtalk     |                                   | data_out              | 32-bit | Out       |

| DIMEtalk     |                                   | data_in_ack           | l-bit  | Out       |

| DIMEtalk     |                                   | data_out_ack          | l-bit  | In        |

| host_clk     | Def. CLK2                         | host_clk              | l-bit  | In        |

| Host Data    |                                   | host_data             | 32-bit | Inout     |

| Host Control |                                   | host_busy             | l-bit  | In        |

| Host Control |                                   | host_empty            | l-bit  | In        |

| Host Control |                                   | host_rw               | l-bit  | Out       |

Table 2: PCI Host Signal Descriptions

| Group        | Туре | Signal<br>Description | Width | Direction |

|--------------|------|-----------------------|-------|-----------|

| Host Control |      | host_asds             | l-bit | In        |

| Host Control |      | host_rwen             | l-bit | Out       |

| Host Control |      | host_int              | l-bit | Out       |

| Host Control |      | host_reset            | l-bit | In        |

| Host Control |      | host_reserved         | l-bit | Out       |

Table 2: PCI Host Signal Descriptions

## **Support Files**

The support file names and devices used are listed in Table 3.

| Name                                                                                                                         | Device<br>Usage         |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| DIMEtalk\library\Edges\pci_host_interface.support\Virtex2\fifo511x32.edn                                                     | Virtex-II               |

| DIMEtalk\library\Edges\pci_host_interface.support\VirtexE\fifo511x32.edn                                                     | Virtex-E                |

| DIMEtalk\library\Edges\pci_host_interface.support\All\pci_host_interface.ngc                                                 | All                     |

| DIMEtalk\library\Edges\pci_host_interface.support\Simulation\pci_host_interface.vhd                                          | Simulation              |

| DIMEtalk\library\Edges\pci_host_interface.support\Simulation_Virtex2\fifo511x32.vhd                                          | Simulation<br>Virtex-II |

| DIMEtalk\library\Edges\pci_host_interface.support\Simulation_VirtexE\fifo511x32.vhd                                          | Simulation<br>Virtex-E  |

| DIMEtalk\library\Edges\pci_host_interface.support\Virtex4\fifo511x32.ngc                                                     | Virtex-4                |

| DIMEtalk\library\Edges\pci_host_interface.support\Virtex4\fifo511x32.vhd                                                     | Virtex-4                |

| DIMEtalk\library\Edges\pci_host_interface.support\Virtex4\fifo511x32core.edn                                                 | Virtex-4                |

| DIMEtalk\library\Edges\pci_host_interface.support\Virtex4\fifo511x32core.vhd                                                 | Virtex-4                |

| DIMEtalk\library\Edges\pci_host_interface.support\Virtex4\fifo511x32core_fifo_generator_v2_2_xst_1.ngc                       | Virtex-4                |

| DIMEtalk\library\Edges\pci_host_interface.support\Virtex4\fifo511x32core_fifo_generator_v2_2_xst_1_blk<br>memdp_v6_2_xst.edn | Virtex-4                |

| DIMEtalk\library\Edges\pci_host_interface.support\Simulation_Virtex4\fifo511x32.vhd                                          | Simulation<br>Virtex-4  |

| DIMEtalk\library\Edges\pci_host_interface.support\Simulation_Virtex4\fifo511x32core.vhd                                      | Simulation<br>Virtex-4  |

Table 3: PCI Host Signal Support Files

# **Component Definition**

Component pci\_host\_interface\_000

Port (

-- reset

reset : in std\_logic;

-- dt\_clk

dt\_clk : in std\_logic;

-- DIMEtalk

data\_in : in std\_logic\_vector(31 downto 0); data\_out : out std\_logic\_vector(31 downto 0); data\_in\_ack : out std\_logic; data\_out\_ack : in std\_logic; -- host clk host clk : in std logic; -- Host Data host\_data : inout std\_logic\_vector(31 downto 0); -- Host Control host\_busy : in std\_logic; host\_empty : in std\_logic; host\_rw : out std\_logic; host\_asds : in std\_logic; host rwen : out std logic; host\_int : out std\_logic; host\_reset : in std\_logic; host reserved : out std logic

### );

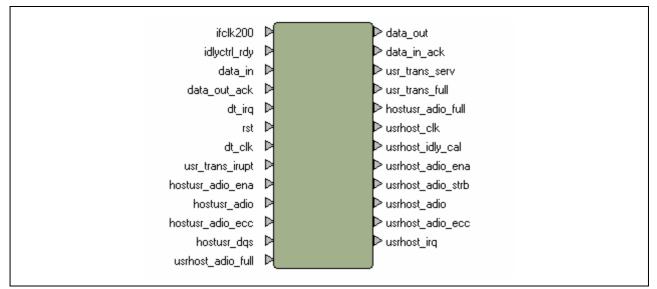

# **PCI-X Host Interface**

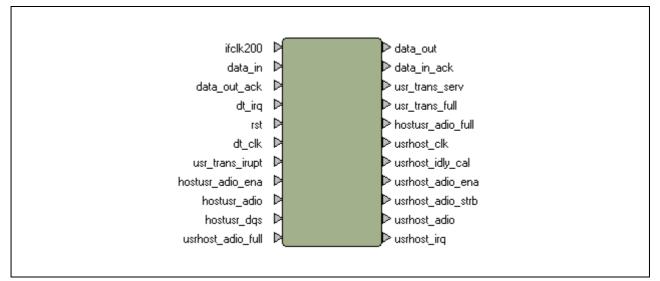

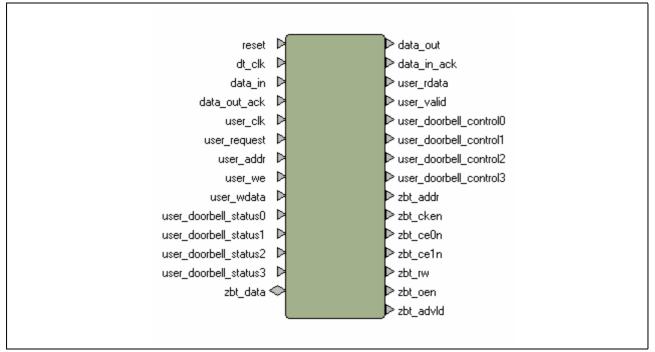

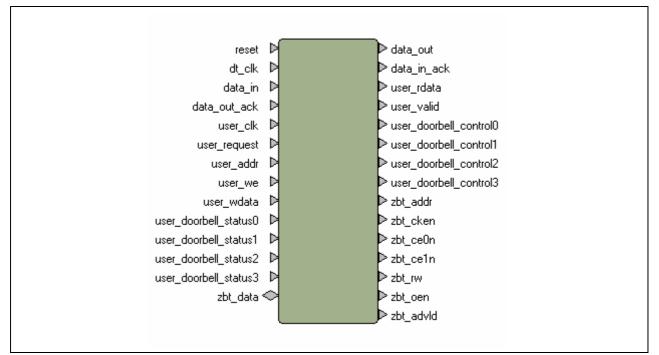

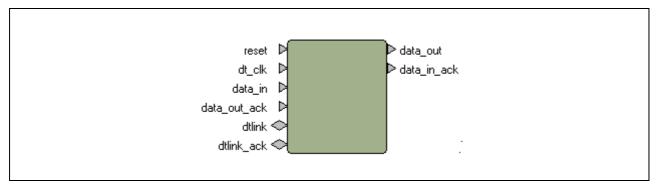

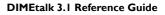

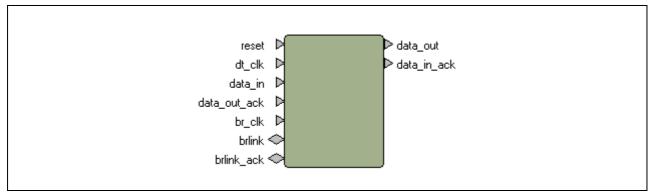

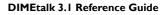

This component, shown in Figure 2, handles the interface between a PCI-X host and a DIMEtalk network on a Nallatech PCI-X card (e.g. BenNUEY-PCI-X). The PCI-X FPGA provides a 200MHz clock source for clocking the PCI-X Host Interface. The component enables communication between the PCI-X and User FPGAs and converts the transferred data into the DIMEtalk clock domain (typically CLK1).

#### Figure 2: PCI-X Host Interface Component

# **S**ignals

The signal descriptions are provided in Table 4.

| Group          | Туре                                  | Signal Description | Width   | Direction |

|----------------|---------------------------------------|--------------------|---------|-----------|

| Reset          | DIMEtalk reset                        | reset              | l-bit   | in        |

| DIMEtalk clock | DIMEtalk network clock.<br>Def. CLK I | dt_clk             | l-bit   | in        |

| Interrupts     |                                       | dt_irq             | 4-bits  | in        |

| DIMEtalk       |                                       | data_in            | 32-bits | in        |

| DIMEtalk       |                                       | data_out           | 32-bits | out       |

| DIMEtalk       |                                       | data_in_ack        | l-bit   | out       |

| DIMEtalk       |                                       | data_out_ack       | l-bit   | in        |

| Host control   |                                       | usr_trans_irupt    | l-bit   | in        |

| Host control   |                                       | usr_trans_serv     | l-bit   | out       |

| Host control   |                                       | hostusr_dqs        | l-bit   | in        |

| Host control   |                                       | hostusr_adio_ena   | l-bit   | in        |

| Host control   |                                       | hostusr_adio_full  | l-bit   | out       |

| Host data      |                                       | hostusr_adio       | 32-bits | in        |

| Host control   |                                       | usrhost_clk        | 4-bits  | out       |

| Host control   |                                       | usrhost_idly_cal   | l-bit   | out       |

| Host control   |                                       | usrhost_adio_ena   | l-bit   | out       |

| Host control   |                                       | usrhost_adio_strb  | l-bit   | out       |

| Host data      |                                       | usrhost_adio       | 32-bits | out       |

| Host control   |                                       | usrhost_irq        | 4-bits  | out       |

| Host control   |                                       | usrhost_adio_full  | l-bit   | in        |

Table 4: PCI-X Host Interface Signal Descriptions

# **Support Files**

The support file names and devices used are listed in Table 5.

| Name                                                                       | Device Usage |

|----------------------------------------------------------------------------|--------------|

| DIMEtalk\library\Edges\pcix_host_interface.support\pcix_host_interface.vhd | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\fifo_64x1024.ngc        | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\infifo64x512.ngc        | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\synfifo32x512.ngc       | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\outfifo32x1024.ngc      | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\user_host_if.vhd        | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\user_host_ctrl.vhd      | Virtex-4     |

Table 5: PCI-X Host Signal Support Files

| Name                                                              | Device Usage |

|-------------------------------------------------------------------|--------------|

| DIMEtalk\library\Edges\pcix_host_interface.support\dt_ctrl_if.vhd | Virtex-4     |

| DIMEtalk\common\resync_rise.vhd                                   | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\rx_iob.vhd     | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\idelay_cal.vhd | Virtex-4     |

| DIMEtalk\library\Edges\pcix_host_interface.support\tx_iob.vhd     | Virtex-4     |

Table 5: PCI-X Host Signal Support Files

## **Component Definition**

component pcix\_host\_interface

generic(

SIM : boolean := FALSE

);

port(

rst : in std\_logic;

ifclk200 : in std\_logic;

-- Group = DIMEtalk

| dt_clk       | : in std_logic;                      |

|--------------|--------------------------------------|

| dt_irq       | : in std_logic_vector( 3 downto 0);  |

| data_in      | : in std_logic_vector(31 downto 0);  |

| data_out     | : out std_logic_vector(31 downto 0); |

| data_in_ack  | : out std_logic;                     |

| data_out_ack | : in std_logic;                      |

-- Group = host interface

-- host <--> user if target data interrupt & service flags

usr\_trans\_irupt : in std\_logic;

| usr_ | _trans_ | _serv | : | out | std_ | logic; |

|------|---------|-------|---|-----|------|--------|

|      |         |       |   |     |      |        |

usr\_trans\_full : out std\_logic;

-- host --> user if (Rx)

| hostusr_dqs       | : in std_logic;                     |

|-------------------|-------------------------------------|

| hostusr_adio_ena  | : in std_logic;                     |

| hostusr_adio      | : in std_logic_vector(31 downto 0); |

| hostusr_adio_full | : out std_logic;                    |

```

-- user --> host if (Tx)

: out std logic vector( 3 downto 0);

usrhost clk

usrhost idly cal

: out std logic;

usrhost_adio_ena

: out std_logic;

usrhost adio strb

: out std logic;

: out std logic vector(31 downto 0);

usrhost adio

usrhost adio full

: in std_logic;

-- user --> host interrupts

: out std_logic_vector( 3 downto 0)

usrhost irq

);

```

# **USB Host Interface**

## **Functional Description**

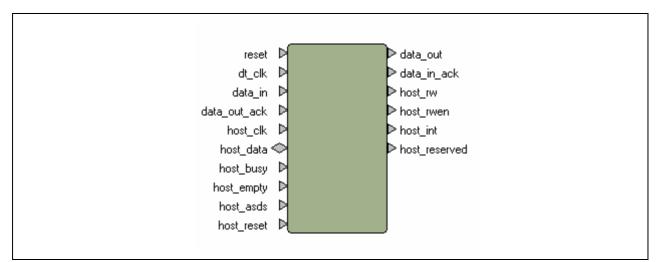

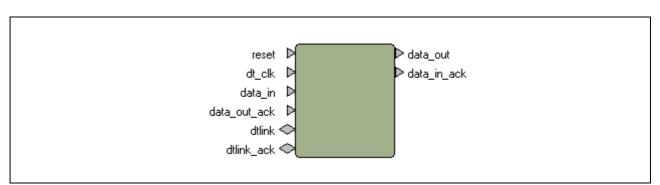

This component handles the interface between a USB module connected host and a DIMEtalk network on Nallatech stand-alone motherboards (e.g. BenNUEY and BenONE). The interface is assumed to be clocked by CLK2. This edge component converts data transferred into the CLK1 domain. On a multi-FPGA motherboard such as the BenNUEY, the Host Data signals should be mapped to PCI\_COMMS(0:31) whilst the Host Control signals should be mapped to PCI\_COMMS(0:31) whilst the Host Control signals should be mapped to PCI\_COMMS(0:31) whilst the Host Control signals should be mapped to BUS(0:31) whilst the Host Control signals should be mapped to LBUS(0:31) whilst the Host Control signals should be mapped to LBUS(0:31) whilst the Host Control signals should be mapped to ADJOUT(0:7). The USB Host Interface signals are shown in Figure 3 and described in Table 6.

Figure 3: USB Host Interface Component

## **S**ignals

The signal descriptions are provided in Table 6.

| Group        | Туре                              | Signal<br>Description | Width   | Direction |

|--------------|-----------------------------------|-----------------------|---------|-----------|

| reset        | DIMEtalk reset                    | reset                 | l-bit   | In        |

| dt_clk       | DIMEtalk network clock. Def. CLKI | dt_clk                | l-bit   | In        |

| DIMEtalk     |                                   | data_in               | 32-bits | In        |

| DIMEtalk     |                                   | data_out              | 32-bits | Out       |

| DIMEtalk     |                                   | data_in_ack           | l-bit   | Out       |

| DIMEtalk     |                                   | data_out_ack          | l-bit   | In        |

| host_clk     | Def. CLK2                         | host_clk              | l-bit   | In        |

| Host Data    |                                   | host_data             | 32-bits | Inout     |

| Host Control |                                   | host_busy             | l-bit   | In        |

| Host Control |                                   | host_empty            | l-bit   | In        |

| Host Control |                                   | host_rw               | l-bit   | Out       |

| Host Control |                                   | host_asds             | l-bit   | In        |

| Host Control |                                   | host_rwen             | l-bit   | Out       |

| Host Control |                                   | host_int              | l-bit   | Out       |

| Host Control |                                   | host_reset            | l-bit   | In        |

| Host Control |                                   | host_reserved         | l-bit   | Out       |

Table 6: USB Host Interface Signal Descriptions

## **Support Files**

The support file names and devices used are listed in Table 7.

| Name                                        | Device Usage |

|---------------------------------------------|--------------|

| components\Edges\Virtex2\fifo511x32.edn     | Virtex-II    |

| components\Edges\VirtexE\fifo511x32.edn     | Virtex-E     |

| components\Edges\All\usb_host_interface.ngc | All          |

Table 7: USB Host Interface Support Files

# **Component Definition**

Component usb\_host\_interface\_000

Port ( -- reset

reset : in std\_logic;

-- dt\_clk

dt\_clk : in std\_logic;

-- DIMEtalk

data in : in std logic vector(31 downto 0); data\_out : out std\_logic\_vector(31 downto 0); data in ack : out std logic; data\_out\_ack : in std\_logic; -- host\_clk host clk : in std logic; -- Host Data host\_data : inout std\_logic\_vector(31 downto 0); -- Host Control host\_busy : in std\_logic; host\_empty : in std\_logic; host rw : out std logic; host\_asds : in std\_logic; host\_rwen : out std\_logic; host int : out std logic; host\_reset : in std\_logic; host\_reserved : out std\_logic

#### );

# **Ethernet Host Interface**

#### **Functional Description**

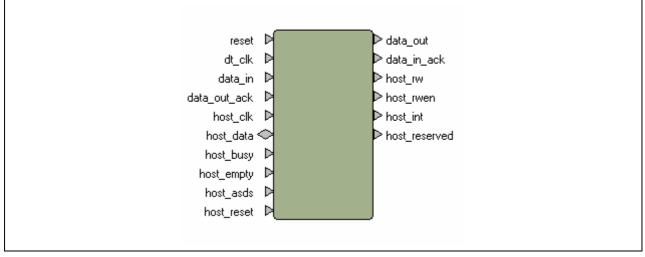

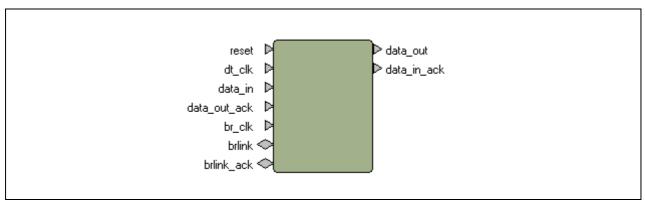

This component handles the interface between an Ethernet module connected host and a DIMEtalk network on Nallatech stand-alone motherboards (e.g. BenNUEY and BenONE). The interface is assumed to be clocked by CLK2. This edge component converts data being transferred into the CLK1 domain. On a multi-FPGA motherboard such as the BenNUEY, the Host Data signals should be mapped to PCI\_COMMS(0:31) whilst the Host Control signals should be mapped to PCI\_COMMS(32:39). If this interface is instantiated on a module plugged into a BenONE carrier card the Host Data signals should be mapped to LBUS(0:31) whilst the Host Control signals should be mapped to ADJOUT(0:7). The Ethernet Host Interface signals are shown in Figure 4 and described in Table 8.

Figure 4: Ethernet Host Interface Component

## **S**ignals

The signal descriptions are provided in Table 8.

| Group        | Туре                               | Signal<br>Description | Width  | Direction |

|--------------|------------------------------------|-----------------------|--------|-----------|

| reset        | DIMEtalk reset                     | reset                 | l-bit  | In        |

| dt_clk       | DIMEtalk network clock. Def. CLK I | dt_clk                | l-bit  | In        |

| DIMEtalk     |                                    | data_in               | 32-bit | In        |

| DIMEtalk     |                                    | data_out              | 32-bit | Out       |

| DIMEtalk     |                                    | data_in_ack           | l-bit  | Out       |

| DIMEtalk     |                                    | data_out_ack          | l-bit  | In        |

| host_clk     | Def. CLK2                          | host_clk              | l-bit  | In        |

| Host Data    |                                    | host_data             | 32-bit | Inout     |

| Host Control |                                    | host_busy             | l-bit  | In        |

| Host Control |                                    | host_empty            | l-bit  | In        |

| Host Control |                                    | host_rw               | l-bit  | Out       |

| Host Control |                                    | host_asds             | l-bit  | In        |

| Host Control |                                    | host_rwen             | l-bit  | Out       |

| Host Control |                                    | host_int              | l-bit  | Out       |

| Host Control |                                    | host_reset            | l-bit  | In        |

| Host Control |                                    | host_reserved         | l-bit  | Out       |

Table 8: Ethernet Host Signal Descriptions

### Support Files

The support file names and devices used are listed in Table 9.

| Name                                             | Device Usage |

|--------------------------------------------------|--------------|

| components\Edges\Virtex2\fifo511x32.edn          | Virtex-II    |

| components\Edges\VirtexE\fifo511x32.edn          | Virtex-E     |

| components\Edges\All\ethernet_host_interface.ngc | All          |

Table 9: Ethernet Host Interface Support Files

# **Component Definition**

Component ethernet\_host\_interface\_000

Port (

-- resetreset : in std\_logic;-- dt\_clkdt\_clk : in std\_logic;

-- DIMEtalk

data in : in std logic vector(31 downto 0); data\_out : out std\_logic\_vector(31 downto 0); data in ack : out std logic; data\_out\_ack : in std\_logic; -- host\_clk host clk : in std logic; -- Host Data host\_data : inout std\_logic\_vector(31 downto 0); -- Host Control host\_busy : in std\_logic; host\_empty : in std\_logic; host\_rw : out std\_logic; host\_asds : in std\_logic; host\_rwen : out std\_logic; host int : out std logic; host\_reset : in std\_logic; host\_reserved : out std\_logic

);

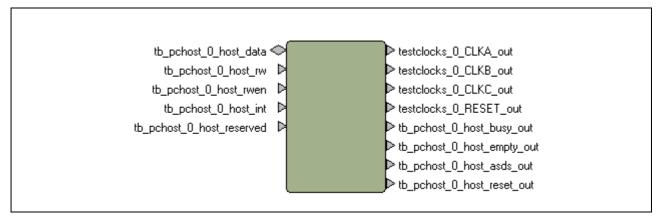

# **Host Testbench**

### **Functional Description**

This component, shown in Figure 5, allows PCI, USB and Ethernet Edge designs to be exercised in simulation. To run a design in simulation users should connect the Host Testbench to the ports on the edge and to the clock driver module component. When a user's VHDL output is opened in the simulator a tcl version of the DIMEtalk runtime API can be used to write into the simulation model. This is contained in the simutils.tcl output file. See "Simulation Support" for more information.

## **S**ignals

The signal descriptions are provided in Table 10.

| Group          | Туре            | Signal Description                                              | Width | Direction |

|----------------|-----------------|-----------------------------------------------------------------|-------|-----------|

| clockreset     | User Connection | testclocks_0_CLKA_out : out STD_LOGIC;                          | 1     | Out       |

|                |                 | testclocks_0_CLKB_out : out STD_LOGIC;                          | I     | Out       |

|                |                 | testclocks_0_CLKC_out : out STD_LOGIC;                          | I     | Out       |

|                |                 | testclocks_0_RESET_out : out STD_LOGIC;                         | I     | Out       |

| host_interface | User Connection | tb_pchost_0_host_data : inout<br>STD_LOGIC_VECTOR(31 downto 0); | 32    | Inout     |

|                |                 | tb_pchost_0_host_busy_out : out<br>STD_LOGIC;                   | I     | Out       |

|                |                 | tb_pchost_0_host_empty_out : out<br>STD_LOGIC;                  | 1     | Out       |

|                |                 | tb_pchost_0_host_rw : in STD_LOGIC;                             | I     | In        |

|                |                 | tb_pchost_0_host_asds_out : out<br>STD_LOGIC;                   | I     | Out       |

|                |                 | tb_pchost_0_host_rwen : in STD_LOGIC;                           | I     | In        |

|                |                 | tb_pchost_0_host_int : in STD_LOGIC;                            | I     | In        |

|                |                 | tb_pchost_0_host_reset_out : out<br>STD_LOGIC;                  | 1     | Out       |

|                |                 | tb_pchost_0_host_reserved : in<br>STD_LOGIC;                    | I     | In        |

Table 10: Host Testbench Signal Descriptions

## Support Files

The support file names and devices used are listed in Table 11.

| Name                                                   | Device Usage |

|--------------------------------------------------------|--------------|

| components \Edges\TestBench.support\All\TestBench.vhd  | All          |

| components \Edges\TestBench.support\All\testclocks.vhd | All          |

| components \Edges\TestBench.support\All\pchost.vhd     | All          |

Table 11: Host Testbench Support Files

## **Component Definition**

port (

testclocks\_0\_CLKA\_out : out STD\_LOGIC; testclocks\_0\_CLKB\_out : out STD\_LOGIC; testclocks\_0\_CLKC\_out : out STD\_LOGIC; testclocks\_0\_RESET\_out : out STD\_LOGIC; tb\_pchost\_0\_host\_data : inout STD\_LOGIC\_VECTOR(31 downto 0); tb\_pchost\_0\_host\_busy\_out : out STD\_LOGIC;

tb\_pchost\_0\_host\_empty\_out : out STD\_LOGIC;

tb\_pchost\_0\_host\_rw : in STD\_LOGIC;

tb\_pchost\_0\_host\_asds\_out : out STD\_LOGIC;

tb\_pchost\_0\_host\_rwen : in STD\_LOGIC;

tb\_pchost\_0\_host\_int : in STD\_LOGIC;

tb\_pchost\_0\_host\_reset\_out : out STD\_LOGIC;

tb\_pchost\_0\_host\_reserved : in STD\_LOGIC

#### );

# **Simulation Support**

The DIMEtalk components instantiate Xilinx DCM and BUFG primitives amongst others. In order to enable functional simulation to be performed Xilinx provides a library of simulation models known as the UNISIM library. The following sections detail how to create and access these libraries.

# Xilinx Simulation Libraries for ModelSim XE

ModelSim XE is a dedicated Xilinx Edition of the tool and therefore provides a pre-compiled UNISIM library. There is no requirement to map to this library as this is built into the tool. This precompiled library is updated with new releases of ISE and can be downloaded from the software resources section of the Xilinx website.

# Xilinx Simulation Libraries for ModelSim SE/PE

As these versions of ModelSim are not linked to any particular technology vendor the Xilinx simulation libraries must be compiled by the user as new versions of ISE become available.

The VHDL source for this library is provided with Xilinx ISE installs, however this code must be complied into a unisim library which the user maps to. Xilinx provide a COMPXLIB utility that automates the compilation of the simulation library. Refer to the Xilinx Synthesis and Verification Design Guide for full details on how to use this utility. A brief summary is provided below:-

1. Compile the unisim library. For example, to compile the unisim library for ModelSim SE for all device types the following command line could be used:-

compxlib -s mti\_pe -arch all -l vhdl -o %XILINX%/vhdl/data/mti -w

The libraries will be created in \$MYLIBDIRECTORY.

2. Map to the UNISIM library

vmap unisim [file join [file normalize \$env(XILINX)] vhdl/data/mti]

When these steps have been performed the simulator will be able to resolve any references to the Xilinx primitives during the elaboration stage.

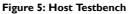

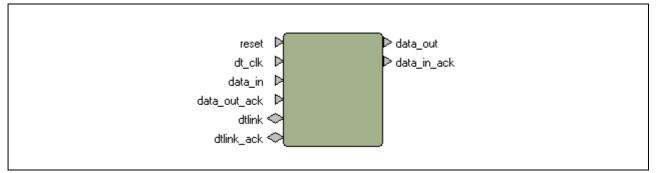

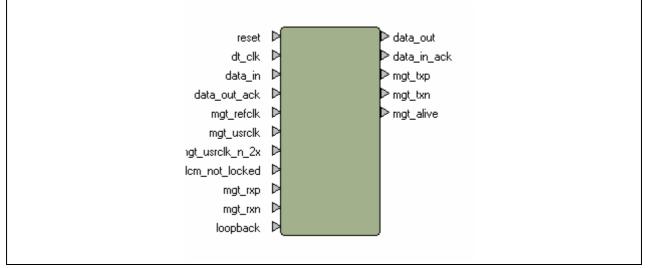

# H100 Host Interface

The H100 Host Interface component, shown in Figure 6, handles communications between the PCI-X host and a DIMEtalk network on H100. Data is converted from the 200MHz interface clock into the DIMEtalk clock domain.

Figure 6: H100 Host Interface Component

## **S**ignals

The signal descriptions are provided in Table 12.

| Group         | Туре                   | Signal Description                                       | Width   | Direction |

|---------------|------------------------|----------------------------------------------------------|---------|-----------|

| PCIxInterface | User Connection        | ifclk200 : in STD_LOGIC;                                 | l-bit   | In        |

| Clocks        |                        | idlyctrl_rdy : in STD_LOGIC;                             | l-bit   | In        |

| DIMEtalk      | DIMEtalk<br>Connection | <pre>data_in : in STD_LOGIC_VECTOR(31 downto 0);</pre>   | 32-bits | In        |

|               |                        | <pre>data_out : out STD_LOGIC_VECTOR(31 downto 0);</pre> | 32-bits | Out       |

|               |                        | data_in_ack : out STD_LOGIC;                             | l-bit   | Out       |

|               |                        | data_out_ack : in STD_LOGIC;                             | l-bit   | In        |

| User Signals  | User Connection        | <pre>dt_irq : in STD_LOGIC_VECTOR(3 downto 0);</pre>     | 4-bits  | In        |

| rst           | Reset Connection       | rst : in STD_LOGIC;                                      | l-bit   | In        |

| dt_clk        | Clock Connection       | dt_clk : in STD_LOGIC;                                   | l-bit   | In        |

Table 12: H100 Host Interface Signal Descriptions

| Group    | Туре            | Signal Description                                      | Width   | Direction |

|----------|-----------------|---------------------------------------------------------|---------|-----------|

| UserPort | User Connection | usr_trans_irupt : in STD_LOGIC;                         | l-bit   | In        |

|          |                 | usr_trans_serv : out STD_LOGIC;                         | l-bit   | Out       |

|          |                 | usr_trans_full : out STD_LOGIC;                         | l-bit   | Out       |

|          |                 | hostusr_adio_full : out STD_LOGIC;                      | l-bit   | Out       |

|          |                 | hostusr_adio_ena : in STD_LOGIC;                        | l-bit   | In        |

|          |                 | hostusr_adio : in STD_LOGIC_VECTOR(31 downto 0);        | 32-bits | In        |

|          |                 | hostusr_adio_ecc : in<br>STD_LOGIC_VECTOR(3 downto 0);  | 4-bits  | In        |

|          |                 | hostusr_dqs : in STD_LOGIC;                             | l-bit   | In        |

|          |                 | usrhost_adio_full : in STD_LOGIC;                       | l-bit   | In        |

|          |                 | usrhost_clk : out STD_LOGIC;                            | l-bit   | Out       |

|          |                 | usrhost_idly_cal : out STD_LOGIC;                       | l-bit   | Out       |

|          |                 | usrhost_adio_ena : out STD_LOGIC;                       | l-bit   | Out       |

|          |                 | usrhost_adio_strb : out STD_LOGIC;                      | l-bit   | Out       |

|          |                 | usrhost_adio : out STD_LOGIC_VECTOR(31 downto 0);       | 32-bits | Out       |

|          |                 | usrhost_adio_ecc : out<br>STD_LOGIC_VECTOR(3 downto 0); | 4-bits  | Out       |

|          |                 | usrhost_irq : out STD_LOGIC_VECTOR(3 downto 0);         | 4-bits  | Out       |

| Table 12: H100 Host Interface | Signal Descriptions |

|-------------------------------|---------------------|

|-------------------------------|---------------------|

# Support Files

The support file names and devices used are listed in Table 13.

| Name                                                                                     | Device Usage |

|------------------------------------------------------------------------------------------|--------------|

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\h100_pcix_host_interface.vhd | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\fifo_64x1024.ngc             | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\infifo64x512.ngc             | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\outfifo32x1024.ngc           | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\synfifo32x512.ngc            | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\h100_user_host_if.vhd        | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\h100_user_host_ctrl.vhd      | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\h100_dt_ctrl_if.vhd          | H100         |

| DIMEtalk\common\resync_rise.vhd                                                          | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\h100_rx_iob.vhd              | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\h100_idelay_cal.vhd          | H100         |

Table 13: H100 Host Interface Support Files

| Name                                                                           | Device Usage |

|--------------------------------------------------------------------------------|--------------|

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\h100_tx_iob.vhd    | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\ecc_encoder_64.vhd | H100         |

| DIMEtalk\library\Edges\h100_pcix_host_interface.support\All\ecc_decoder_64.vhd | H100         |

Table 13: H100 Host Interface Support Files

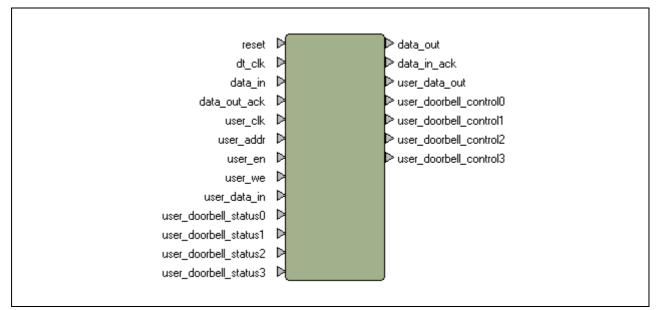

# I.2 Basic Internal FPGA Nodes

# Block RAM Node

## **Functional Description**

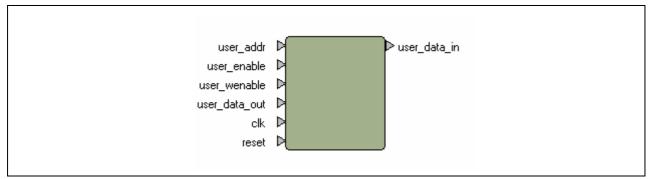

The block RAM component creates an area of shared memory. This component is generic in terms of size, and the user specifies a parameter which infers the correct depth. The depth of the generic version is limited by the available resources on the targeted device. The memory is dual port and accessible from the DIMEtalk side (by other DIMEtalk nodes) and the user side. Each has a separate clock although both are wired by default to CLKI. The block RAM signal names are shown in Figure 7 and described in Table 14.

Figure 7: Block RAM Node Component

### **Extended Doorbell**

There are four doorbell status inputs and four doorbell control outputs. The status inputs can be used to trap a change of state on an input whilst the control outputs can be used as a trigger for aspects of a user's design. For more information on packets see "Request Packet Type 10 (Doorbell class)".

### **Signals**

The signal descriptions are provided in Table 14.

| Group | Туре           | Signal Description | Width | Direction |

|-------|----------------|--------------------|-------|-----------|

| reset | DIMEtalk reset | reset              | l-bit | In        |

Table 14: Block RAM Signal Descriptions

| Group         | Туре                                  | Signal Description     | Width    | Direction |

|---------------|---------------------------------------|------------------------|----------|-----------|

| dt_clk        | DIMEtalk network clock. Def.ault CLKI | dt_clk                 | l-bit    | In        |

| DIMEtalk      |                                       | data_in                | 32-bits  | In        |

| DIMEtalk      |                                       | data_out               | 32-bits  | Out       |

| DIMEtalk      |                                       | data_in_ack            | l-bit    | Out       |

| DIMEtalk      |                                       | data_out_ack           | l-bit    | In        |

| User_clk      | User clock. Def. CLK I                | user_clk               | l-bit    | In        |

| UserInterface |                                       | User_addr              | l 6-bits | In        |

| UserInterface |                                       | User_en                | l-bit    | In        |

| UserInterface |                                       | User_we                | l-bit    | In        |

| UserInterface |                                       | User_data_in           | 32-bits  | In        |

| UserInterface |                                       | User_data_out          | 32-bits  | Out       |

| Doorbells     |                                       | user_doorbell_status0  | l-bit    | In        |